Celerity

Open-Source RISC-V Tiered Accelerator Fabric SoC.

Celerity is an accelerator-centric system-on-chip (SoC) which uses a tiered accelerator fabric to improve energy efficiency in the context of high-performance embedded systems.

The SoC is a 5x5 mm2 385 M-transistor chip in TSMC 16 nm designed and implemented by a modest team of over 20 students and faculty from the University of Michigan, Cornell University, and the Bespoke Silicon Group (now at U. Washington) as part of the DARPA Circuit Realization At Faster Timescales (CRAFT) program.

Celerity currently holds the world record for RISC-V performance; 500B RISC-V instructions per second, beating prior records by 100X.

SoC Structure

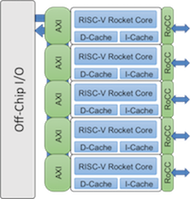

General Purpose Tier

A few fully featured RISC-V processors capable of running general-purpose software including an operating system. Modified version of Berkeley Rocket core.

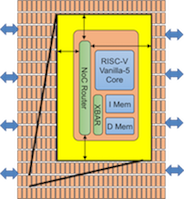

Massive Parallel Tier

A manycore comprising hundreds of lightweight RISC-V processors, a distributed shared memory system, and a mesh-based interconnect.

Specialization Tier

Application-specific accelerators (possibly generated using high-level synthesis).

Related Links

Publication

Please cite following paper if you find our research helpful:

1

2

3

4

5

6

7

8

9

10

@article{davidson2018celerity,

title={The Celerity open-source 511-core RISC-V tiered accelerator fabric: Fast architectures and design methodologies for fast chips},

author={Davidson, Scott and Xie, Shaolin and Torng, Christopher and Al-Hawai, Khalid and Rovinski, Austin and Ajayi, Tutu and Vega, Luis and Zhao, Chun and Zhao, Ritchie and Dai, Steve and others},

journal={IEEE Micro},

volume={38},

number={2},

pages={30--41},

year={2018},

publisher={IEEE}

}

2019

- A 1.4 GHz 695 Giga Risc-V Inst/s 496-Core Manycore Processor With Mesh On-Chip Network and an All-Digital Synthesized PLL in 16nm CMOSIn 2019 Symposium on VLSI Circuits, 2019

2019

- Evaluating Celerity: A 16-nm 695 Giga-RISC-V Instructions/s Manycore Processor With Synthesizable PLLIEEE Solid-State Circuits Letters, 2019

2018

- The Celerity open-source 511-core RISC-V tiered accelerator fabric: Fast architectures and design methodologies for fast chipsIEEE Micro, 2018

2017

- Celerity: An open source RISC-V tiered accelerator fabricIn Hot Chips: A Symposium on High Performance Chips, 2017

2018

- The BaseJump Manycore Accelerator NetworkarXiv preprint arXiv:1808.00650, 2018

2017

- Experiences Using the RISC-V Ecosystem to Design an Accelerator-Centric SoC in TSMC 16nm2017