MaPU

A Mathematical Computing Architecture with VLIW and CGRA features.

MaPU (Mathematical Processing Unit) is a novel architecture targeting data-intensive computing with great power efficiency and sustained computation throughput.

To achieve this goal, MaPU uses mathematical formulates style program model, directly mapped data path on CGRA fabric and groundbreaking memory system that supports simultaneous row-major and column major matrix with the same layout.

The Function Unit (FU) are connected via a cross bar to form a CGRA farbic

Toolchains

MaPU toolchain includes assembler/disassembler, compiler, simulator etc., for both scalar pipeline and micro-code pipeline. Complete source code can be found at https://github.com/mapu/toolchains.git.

| Tool name | Based Open Source Framework |

|---|---|

| Compiler for State Machine based language | Ragel &Bison & LLVM |

| C compiler for Scalar Pipeline | Clang & LLVM |

| Assembler /Disassembler | Ragel & Bison & LLVM |

| Linker | Binutils Gold |

| Debugger for Scalar Pipeline | GDB |

| Simulator ( Scalar & Microcode ) | Gem5 |

| Emulator | OpenOCD |

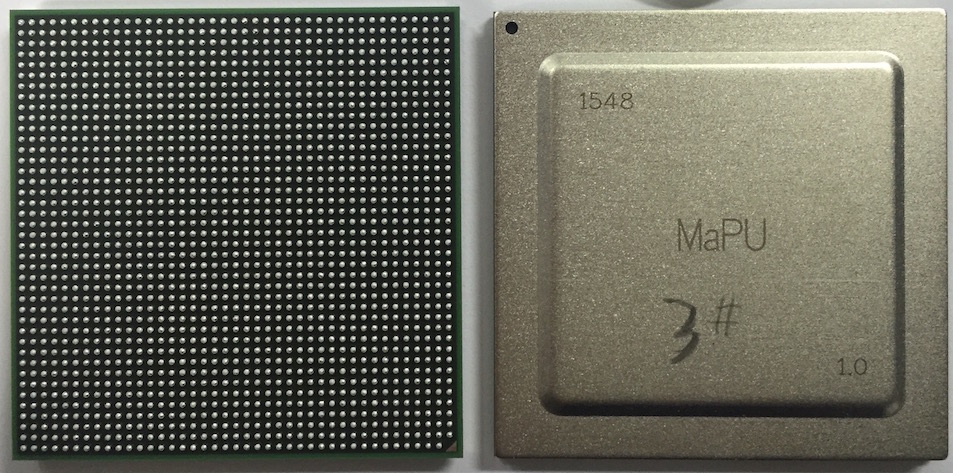

Prototype Chip

Left: Layout of a MaPU Core. Right: Packaged 40nm chip.

Chip Performance

Performance chart.

Publication

Please cite our HPCA’16 paper if you are inspired our work:

1

2

3

4

5

6

7

8

@inproceedings{wang2016mapu,

title={MaPU: A novel mathematical computing architecture},

author={Wang, Donglin and Xie, Shaolin and others},

booktitle={2016 IEEE International Symposium on High Performance Computer Architecture (HPCA)},

pages={457--468},

year={2016},

organization={IEEE}

}

Patents

2018

- Parallel filtering method and corresponding apparatusMay 2018US Patent 9,966,932

2016

- Methods and devices for multi-granularity parallel FFT butterfly computationFeb 2016US Patent 9,262,378

- Data access method and device for parallel FFT computationApr 2016US Patent 9,317,481

- Parallel bit reversal devices and methodsFeb 2016US Patent 9,268,744

2015

- Multi-granularity parallel storage systemOct 2015US Patent 9,171,593

- Multi-granularity parallel storage system and storageSep 2015US Patent 9,146,696